SPIM — Serial peripheral interface master with EasyDMA

The SPI master can communicate with multiple SPI slaves using individual chip select signals for each slave.

The the main features of SPIM are:

- EasyDMA direct transfer to/from RAM

- SPI mode 0-3

- Individual selection of I/O pins

- Optional D/CX output line for distinguishing between command and data bytes

SPI master transaction sequence

An SPI master transaction is started by triggering the START task. When started, a number of bytes will be transmitted/received on MOSI/MISO.

The following figure illustrates an SPI master transaction.

The ENDTX is generated when all bytes in buffer TXD.PTR are transmitted. The number of bytes in the transmit buffer is specified in register TXD.MAXCNT. The ENDRX event will be generated when buffer RXD.PTR is full, that is when the number of bytes specified in register RXD.MAXCNT have been received. The transaction stops automatically after all bytes have been transmitted/received. When the maximum number of bytes in receive buffer is larger than the number of bytes in the transmit buffer, the contents of register ORC will be transmitted after the last byte in the transmit buffer has been transmitted.

The END event will be generated after both the ENDRX and ENDTX events have been generated.

The SPI master can be stopped by triggering the STOP task. A STOPPED event is generated when the SPI master has stopped. If the STOP task is triggered in the middle of a transaction, SPIM will complete the transmission/reception of the current byte before stopping. The STOPPED event is generated even if the STOP task is triggered while there is no ongoing transaction.

If the ENDTX event has not already been generated when the SPI master has come to a stop, the ENDTX event will be generated even if all bytes in the buffer TXD.PTR have not been transmitted.

If the ENDRX event has not already been generated when the SPI master has come to a stop, the ENDRX event will be generated even if the buffer RXD.PTR is not full.

A transaction can be suspended and resumed using the SUSPEND and RESUME tasks, receptively. When the SUSPEND task is triggered, the SPI master will complete transmitting and receiving the current ongoing byte before it is suspended.

D/CX functionality

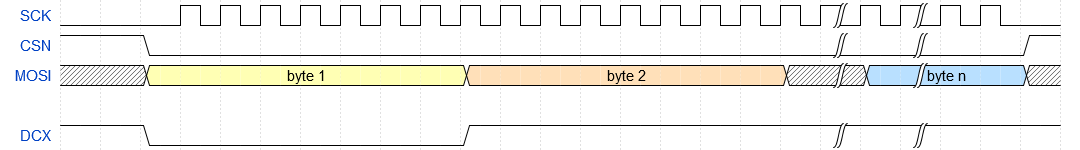

Some SPI slaves, for example display drivers, require an additional signal from the SPI master to distinguish between command and data bytes. For display drivers this line is often called D/CX.

The SPIM provides support for such a D/CX output line. The D/CX line is set low during transmission of command bytes and high during transmission of data bytes.

The D/CX pin number is selected using PSELDCX and the number of command bytes preceding the data bytes is configured using DCXCNT.

It is not allowed to write to the DCXCNT during an ongoing transmission.

The following figure shows the use of D/CX, using SPIM.DCXCNT=1.

Pin configuration

The SCK, CSN, DCX, MOSI, and MISO signals associated with the SPIM are mapped to physical pins according to the configuration specified in the PSEL.n registers.

The contents of registers PSEL.SCK, PSEL.CSN, PSELDCX, PSEL.MOSI, and PSEL.MISO are only used when the SPIM is enabled and retained only as long as the device is in System ON mode. The PSEL.n registers can only be configured when the SPIM is disabled. Enabling/disabling is done using register ENABLE.

To ensure correct behavior, the pins used by the SPIM must be configured in the GPIO peripheral as described in GPIO configuration before the SPIM is enabled. Make sure to activate the dedicated peripheral setting of the GPIO pin. See GPIO — General purpose input/output for details on how to assign pins between cores, peripherals, or subsystems. For pin recommendations, see Pin assignments.

Only one peripheral can be assigned to drive a particular GPIO pin at a time. Failing to do so may result in unpredictable behavior.

| SPI master signal | SPI master pin | Direction | Output value |

|---|---|---|---|

| SCK | As specified in PSEL.SCK | Output | Same as CONFIG.CPOL |

| CSN | As specified in PSEL.CSN | Output | Same as CONFIG.CPOL |

| DCX | As specified in PSELDCX | Output | 1 |

| MOSI | As specified in PSEL.MOSI | Output | 0 |

| MISO | As specified in PSEL.MISO | Input | Not applicable |

Some SPIM instances do not support automatic control of CSN, and for those the available GPIO pins need to be used to control CSN directly. See Instances for information about what features are supported in the various SPIM instances.

The SPIM supports SPI modes 0 through 3. The clock polarity (CPOL) and the clock phase (CPHA) are configured in register CONFIG.

| Mode | Clock polarity | Clock phase |

|---|---|---|

| CPOL | CPHA | |

| SPI_MODE0 | 0 (Active High) | 0 (Leading) |

| SPI_MODE1 | 0 (Active High) | 1 (Trailing) |

| SPI_MODE2 | 1 (Active Low) | 0 (Leading) |

| SPI_MODE3 | 1 (Active Low) | 1 (Trailing) |

Shared resources

The SPI shares registers and other resources with other peripherals that have the same ID as the SPI. Therefore, the user must disable all peripherals that have the same ID as the SPI before the SPI can be configured and used.

Disabling a peripheral that has the same ID as the SPI will not reset any of the registers that are shared with the SPI. It is therefore important to configure all relevant SPI registers explicitly to secure that it operates correctly.

See the Instantiation table in Peripherals for details on peripherals and their IDs.

EasyDMA

SPIM implements EasyDMA for accessing RAM without CPU involvement.

For detailed information regarding the use of EasyDMA, see EasyDMA.

The .PTR and .MAXCNT registers are double-buffered. They can be updated and prepared for the next transmission immediately after having received the STARTED event.

The SPI master will automatically stop transmitting after TXD.MAXCNT bytes have been transmitted and RXD.MAXCNT bytes have been received. If RXD.MAXCNT is larger than TXD.MAXCNT, the remaining transmitted bytes will contain the value defined in the ORC register. If TXD.MAXCNT is larger than RXD.MAXCNT, the additional received bytes will be discarded.

The ENDRX/ENDTX events indicate that EasyDMA has finished accessing respectively the RX/TX buffer in RAM. The END event gets generated when both RX and TX are finished accessing the buffers in RAM.

If several AHB bus masters try to access the same AHB slave at the same time, AHB bus congestion might occur, and the behavior of the EasyDMA channel will depend on the SPIM instance. Refer to Instances for information about what behavior is supported in the various instances.

Low power

To ensure lowest possible power consumption when the peripheral is not needed stop and disable SPIM.

The STOP task may not be always needed (the peripheral might already be stopped), but if it is sent, software shall wait until the STOPPED event was received as a response before disabling the peripheral through the ENABLE register.

Registers

| Base address | Domain | Peripheral | Instance | Secure mapping | DMA security | Description | Configuration | |

|---|---|---|---|---|---|---|---|---|

|

0x50008000 |

APPLICATION | SPIM |

SPIM0 : S |

US |

SA |

SPI master 0 |

Not supported: > 8 Mbps data rate, CSNPOL register, DCX functionality, IFTIMING.x registers, hardware CSN control (PSEL.CSN), stalling mechanism during AHB bus contention |

|

|

0x50009000 |

APPLICATION | SPIM |

SPIM1 : S |

US |

SA |

SPI master 1 |

Not supported: > 8 Mbps data rate, CSNPOL register, DCX functionality, IFTIMING.x registers, hardware CSN control (PSEL.CSN), stalling mechanism during AHB bus contention |

|

|

0x5000A000 |

APPLICATION | SPIM |

SPIM4 : S |

US |

SA |

SPI master 4 (high-speed) |

Up to 32 Mbps SPI when using dedicated pins |

|

|

0x5000B000 |

APPLICATION | SPIM |

SPIM2 : S |

US |

SA |

SPI master 2 |

Not supported: > 8 Mbps data rate, CSNPOL register, DCX functionality, IFTIMING.x registers, hardware CSN control (PSEL.CSN), stalling mechanism during AHB bus contention |

|

|

0x5000C000 |

APPLICATION | SPIM |

SPIM3 : S |

US |

SA |

SPI master 3 |

Not supported: > 8 Mbps data rate, CSNPOL register, DCX functionality, IFTIMING.x registers, hardware CSN control (PSEL.CSN), stalling mechanism during AHB bus contention |

|

| 0x41013000 | NETWORK | SPIM | SPIM0 | NS | NA |

SPI master 0 |

Not supported: > 8 Mbps data rate, IFTIMING.x registers, hardware CSN control (PSEL.CSN), stalling mechanism during AHB bus contention |

|

| Register | Offset | Security | Description | |

|---|---|---|---|---|

| TASKS_START | 0x010 |

Start SPI transaction |

||

| TASKS_STOP | 0x014 |

Stop SPI transaction |

||

| TASKS_SUSPEND | 0x01C |

Suspend SPI transaction |

||

| TASKS_RESUME | 0x020 |

Resume SPI transaction |

||

| SUBSCRIBE_START | 0x090 |

Subscribe configuration for task START |

||

| SUBSCRIBE_STOP | 0x094 |

Subscribe configuration for task STOP |

||

| SUBSCRIBE_SUSPEND | 0x09C |

Subscribe configuration for task SUSPEND |

||

| SUBSCRIBE_RESUME | 0x0A0 |

Subscribe configuration for task RESUME |

||

| EVENTS_STOPPED | 0x104 |

SPI transaction has stopped |

||

| EVENTS_ENDRX | 0x110 |

End of RXD buffer reached |

||

| EVENTS_END | 0x118 |

End of RXD buffer and TXD buffer reached |

||

| EVENTS_ENDTX | 0x120 |

End of TXD buffer reached |

||

| EVENTS_STARTED | 0x14C |

Transaction started |

||

| PUBLISH_STOPPED | 0x184 |

Publish configuration for event STOPPED |

||

| PUBLISH_ENDRX | 0x190 |

Publish configuration for event ENDRX |

||

| PUBLISH_END | 0x198 |

Publish configuration for event END |

||

| PUBLISH_ENDTX | 0x1A0 |

Publish configuration for event ENDTX |

||

| PUBLISH_STARTED | 0x1CC |

Publish configuration for event STARTED |

||

| SHORTS | 0x200 |

Shortcuts between local events and tasks |

||

| INTENSET | 0x304 |

Enable interrupt |

||

| INTENCLR | 0x308 |

Disable interrupt |

||

| STALLSTAT | 0x400 |

Stall status for EasyDMA RAM accesses. The fields in this register are set to STALL by hardware whenever a stall occurres and can be cleared (set to NOSTALL) by the CPU. |

||

| ENABLE | 0x500 |

Enable SPIM |

||

| PSEL.SCK | 0x508 |

Pin select for SCK |

||

| PSEL.MOSI | 0x50C |

Pin select for MOSI signal |

||

| PSEL.MISO | 0x510 |

Pin select for MISO signal |

||

| PSEL.CSN | 0x514 |

Pin select for CSN |

||

| FREQUENCY | 0x524 |

SPI frequency. Accuracy depends on the HFCLK source selected. |

||

| RXD.PTR | 0x534 |

Data pointer |

||

| RXD.MAXCNT | 0x538 |

Maximum number of bytes in receive buffer |

||

| RXD.AMOUNT | 0x53C |

Number of bytes transferred in the last transaction |

||

| RXD.LIST | 0x540 |

EasyDMA list type |

||

| TXD.PTR | 0x544 |

Data pointer |

||

| TXD.MAXCNT | 0x548 |

Number of bytes in transmit buffer |

||

| TXD.AMOUNT | 0x54C |

Number of bytes transferred in the last transaction |

||

| TXD.LIST | 0x550 |

EasyDMA list type |

||

| CONFIG | 0x554 |

Configuration register |

||

| IFTIMING.RXDELAY | 0x560 |

Sample delay for input serial data on MISO |

||

| IFTIMING.CSNDUR | 0x564 |

Minimum duration between edge of CSN and edge of SCK. When SHORTS.END_START is used, this is also the minimum duration CSN must stay high between transactions. |

||

| CSNPOL | 0x568 |

Polarity of CSN output |

||

| PSELDCX | 0x56C |

Pin select for DCX signal |

||

| DCXCNT | 0x570 |

DCX configuration |

||

| ORC | 0x5C0 |

Byte transmitted after TXD.MAXCNT bytes have been transmitted in the case when RXD.MAXCNT is greater than TXD.MAXCNT |

||

TASKS_START

Address offset: 0x010

Start SPI transaction

| Bit number | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ID | A | ||||||||||||||||||||||||||||||||||

| Reset 0x00000000 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| ID | R/W | Field | Value ID | Value | Description | ||||||||||||||||||||||||||||||

| A | W |

TASKS_START |

Start SPI transaction |

||||||||||||||||||||||||||||||||

|

Trigger |

1 |

Trigger task |

|||||||||||||||||||||||||||||||||

TASKS_STOP

Address offset: 0x014

Stop SPI transaction

| Bit number | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ID | A | ||||||||||||||||||||||||||||||||||

| Reset 0x00000000 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| ID | R/W | Field | Value ID | Value | Description | ||||||||||||||||||||||||||||||

| A | W |

TASKS_STOP |

Stop SPI transaction |

||||||||||||||||||||||||||||||||

|

Trigger |

1 |

Trigger task |

|||||||||||||||||||||||||||||||||

TASKS_SUSPEND

Address offset: 0x01C

Suspend SPI transaction

| Bit number | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ID | A | ||||||||||||||||||||||||||||||||||

| Reset 0x00000000 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| ID | R/W | Field | Value ID | Value | Description | ||||||||||||||||||||||||||||||

| A | W |

TASKS_SUSPEND |

Suspend SPI transaction |

||||||||||||||||||||||||||||||||

|

Trigger |

1 |

Trigger task |

|||||||||||||||||||||||||||||||||

TASKS_RESUME

Address offset: 0x020

Resume SPI transaction

| Bit number | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ID | A | ||||||||||||||||||||||||||||||||||

| Reset 0x00000000 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| ID | R/W | Field | Value ID | Value | Description | ||||||||||||||||||||||||||||||

| A | W |

TASKS_RESUME |

Resume SPI transaction |

||||||||||||||||||||||||||||||||

|

Trigger |

1 |

Trigger task |

|||||||||||||||||||||||||||||||||

SUBSCRIBE_START

Address offset: 0x090

Subscribe configuration for task START

| Bit number | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ID | B | A | A | A | A | A | A | A | A | ||||||||||||||||||||||||||

| Reset 0x00000000 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| ID | R/W | Field | Value ID | Value | Description | ||||||||||||||||||||||||||||||

| A | RW |

CHIDX |

[255..0] |

DPPI channel that task START will subscribe to |

|||||||||||||||||||||||||||||||

| B | RW |

EN |

|||||||||||||||||||||||||||||||||

|

Disabled |

0 |

Disable subscription |

|||||||||||||||||||||||||||||||||

|

Enabled |

1 |

Enable subscription |

|||||||||||||||||||||||||||||||||

SUBSCRIBE_STOP

Address offset: 0x094

Subscribe configuration for task STOP

| Bit number | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ID | B | A | A | A | A | A | A | A | A | ||||||||||||||||||||||||||

| Reset 0x00000000 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| ID | R/W | Field | Value ID | Value | Description | ||||||||||||||||||||||||||||||

| A | RW |

CHIDX |

[255..0] |

DPPI channel that task STOP will subscribe to |

|||||||||||||||||||||||||||||||

| B | RW |

EN |

|||||||||||||||||||||||||||||||||

|

Disabled |

0 |

Disable subscription |

|||||||||||||||||||||||||||||||||

|

Enabled |

1 |

Enable subscription |

|||||||||||||||||||||||||||||||||

SUBSCRIBE_SUSPEND

Address offset: 0x09C

Subscribe configuration for task SUSPEND

| Bit number | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ID | B | A | A | A | A | A | A | A | A | ||||||||||||||||||||||||||

| Reset 0x00000000 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| ID | R/W | Field | Value ID | Value | Description | ||||||||||||||||||||||||||||||

| A | RW |

CHIDX |

[255..0] |

DPPI channel that task SUSPEND will subscribe to |

|||||||||||||||||||||||||||||||

| B | RW |

EN |

|||||||||||||||||||||||||||||||||

|

Disabled |

0 |

Disable subscription |

|||||||||||||||||||||||||||||||||

|

Enabled |

1 |

Enable subscription |

|||||||||||||||||||||||||||||||||

SUBSCRIBE_RESUME

Address offset: 0x0A0

Subscribe configuration for task RESUME

| Bit number | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ID | B | A | A | A | A | A | A | A | A | ||||||||||||||||||||||||||

| Reset 0x00000000 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| ID | R/W | Field | Value ID | Value | Description | ||||||||||||||||||||||||||||||

| A | RW |

CHIDX |

[255..0] |

DPPI channel that task RESUME will subscribe to |

|||||||||||||||||||||||||||||||

| B | RW |

EN |

|||||||||||||||||||||||||||||||||

|

Disabled |

0 |

Disable subscription |

|||||||||||||||||||||||||||||||||

|

Enabled |

1 |

Enable subscription |

|||||||||||||||||||||||||||||||||

EVENTS_STOPPED

Address offset: 0x104

SPI transaction has stopped

| Bit number | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ID | A | ||||||||||||||||||||||||||||||||||

| Reset 0x00000000 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| ID | R/W | Field | Value ID | Value | Description | ||||||||||||||||||||||||||||||

| A | RW |

EVENTS_STOPPED |

SPI transaction has stopped |

||||||||||||||||||||||||||||||||

|

NotGenerated |

0 |

Event not generated |

|||||||||||||||||||||||||||||||||

|

Generated |

1 |

Event generated |

|||||||||||||||||||||||||||||||||

EVENTS_ENDRX

Address offset: 0x110

End of RXD buffer reached

| Bit number | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ID | A | ||||||||||||||||||||||||||||||||||

| Reset 0x00000000 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| ID | R/W | Field | Value ID | Value | Description | ||||||||||||||||||||||||||||||

| A | RW |

EVENTS_ENDRX |

End of RXD buffer reached |

||||||||||||||||||||||||||||||||

|

NotGenerated |

0 |

Event not generated |

|||||||||||||||||||||||||||||||||

|

Generated |

1 |

Event generated |

|||||||||||||||||||||||||||||||||

EVENTS_END

Address offset: 0x118

End of RXD buffer and TXD buffer reached

| Bit number | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ID | A | ||||||||||||||||||||||||||||||||||

| Reset 0x00000000 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| ID | R/W | Field | Value ID | Value | Description | ||||||||||||||||||||||||||||||

| A | RW |

EVENTS_END |

End of RXD buffer and TXD buffer reached |

||||||||||||||||||||||||||||||||

|

NotGenerated |

0 |

Event not generated |

|||||||||||||||||||||||||||||||||

|

Generated |

1 |

Event generated |

|||||||||||||||||||||||||||||||||

EVENTS_ENDTX

Address offset: 0x120

End of TXD buffer reached

| Bit number | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ID | A | ||||||||||||||||||||||||||||||||||

| Reset 0x00000000 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| ID | R/W | Field | Value ID | Value | Description | ||||||||||||||||||||||||||||||

| A | RW |

EVENTS_ENDTX |

End of TXD buffer reached |

||||||||||||||||||||||||||||||||

|

NotGenerated |

0 |

Event not generated |

|||||||||||||||||||||||||||||||||

|

Generated |

1 |

Event generated |

|||||||||||||||||||||||||||||||||

EVENTS_STARTED

Address offset: 0x14C

Transaction started

| Bit number | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ID | A | ||||||||||||||||||||||||||||||||||

| Reset 0x00000000 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| ID | R/W | Field | Value ID | Value | Description | ||||||||||||||||||||||||||||||

| A | RW |

EVENTS_STARTED |

Transaction started |

||||||||||||||||||||||||||||||||

|

NotGenerated |

0 |

Event not generated |

|||||||||||||||||||||||||||||||||

|

Generated |

1 |

Event generated |

|||||||||||||||||||||||||||||||||

PUBLISH_STOPPED

Address offset: 0x184

Publish configuration for event STOPPED

| Bit number | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ID | B | A | A | A | A | A | A | A | A | ||||||||||||||||||||||||||

| Reset 0x00000000 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| ID | R/W | Field | Value ID | Value | Description | ||||||||||||||||||||||||||||||

| A | RW |

CHIDX |

[255..0] |

DPPI channel that event STOPPED will publish to. |

|||||||||||||||||||||||||||||||

| B | RW |

EN |

|||||||||||||||||||||||||||||||||

|

Disabled |

0 |

Disable publishing |

|||||||||||||||||||||||||||||||||

|

Enabled |

1 |

Enable publishing |

|||||||||||||||||||||||||||||||||

PUBLISH_ENDRX

Address offset: 0x190

Publish configuration for event ENDRX

| Bit number | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ID | B | A | A | A | A | A | A | A | A | ||||||||||||||||||||||||||

| Reset 0x00000000 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| ID | R/W | Field | Value ID | Value | Description | ||||||||||||||||||||||||||||||

| A | RW |

CHIDX |

[255..0] |

DPPI channel that event ENDRX will publish to. |

|||||||||||||||||||||||||||||||

| B | RW |

EN |

|||||||||||||||||||||||||||||||||

|

Disabled |

0 |

Disable publishing |

|||||||||||||||||||||||||||||||||

|

Enabled |

1 |

Enable publishing |

|||||||||||||||||||||||||||||||||

PUBLISH_END

Address offset: 0x198

Publish configuration for event END

| Bit number | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ID | B | A | A | A | A | A | A | A | A | ||||||||||||||||||||||||||

| Reset 0x00000000 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| ID | R/W | Field | Value ID | Value | Description | ||||||||||||||||||||||||||||||

| A | RW |

CHIDX |

[255..0] |

DPPI channel that event END will publish to. |

|||||||||||||||||||||||||||||||

| B | RW |

EN |

|||||||||||||||||||||||||||||||||

|

Disabled |

0 |

Disable publishing |

|||||||||||||||||||||||||||||||||

|

Enabled |

1 |

Enable publishing |

|||||||||||||||||||||||||||||||||

PUBLISH_ENDTX

Address offset: 0x1A0

Publish configuration for event ENDTX

| Bit number | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ID | B | A | A | A | A | A | A | A | A | ||||||||||||||||||||||||||

| Reset 0x00000000 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| ID | R/W | Field | Value ID | Value | Description | ||||||||||||||||||||||||||||||

| A | RW |

CHIDX |

[255..0] |

DPPI channel that event ENDTX will publish to. |

|||||||||||||||||||||||||||||||

| B | RW |

EN |

|||||||||||||||||||||||||||||||||

|

Disabled |

0 |

Disable publishing |

|||||||||||||||||||||||||||||||||

|

Enabled |

1 |

Enable publishing |

|||||||||||||||||||||||||||||||||

PUBLISH_STARTED

Address offset: 0x1CC

Publish configuration for event STARTED

| Bit number | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ID | B | A | A | A | A | A | A | A | A | ||||||||||||||||||||||||||

| Reset 0x00000000 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| ID | R/W | Field | Value ID | Value | Description | ||||||||||||||||||||||||||||||

| A | RW |

CHIDX |

[255..0] |

DPPI channel that event STARTED will publish to. |

|||||||||||||||||||||||||||||||

| B | RW |

EN |

|||||||||||||||||||||||||||||||||

|

Disabled |

0 |

Disable publishing |

|||||||||||||||||||||||||||||||||

|

Enabled |

1 |

Enable publishing |

|||||||||||||||||||||||||||||||||

SHORTS

Address offset: 0x200

Shortcuts between local events and tasks

| Bit number | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ID | A | ||||||||||||||||||||||||||||||||||

| Reset 0x00000000 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| ID | R/W | Field | Value ID | Value | Description | ||||||||||||||||||||||||||||||

| A | RW |

END_START |

|||||||||||||||||||||||||||||||||

|

Disabled |

0 |

Disable shortcut |

|||||||||||||||||||||||||||||||||

|

Enabled |

1 |

Enable shortcut |

|||||||||||||||||||||||||||||||||

INTENSET

Address offset: 0x304

Enable interrupt

| Bit number | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ID | E | D | C | B | A | ||||||||||||||||||||||||||||||

| Reset 0x00000000 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| ID | R/W | Field | Value ID | Value | Description | ||||||||||||||||||||||||||||||

| A | RW |

STOPPED |

Write '1' to enable interrupt for event STOPPED |

||||||||||||||||||||||||||||||||

|

Set |

1 |

Enable |

|||||||||||||||||||||||||||||||||

|

Disabled |

0 |

Read: Disabled |

|||||||||||||||||||||||||||||||||

|

Enabled |

1 |

Read: Enabled |

|||||||||||||||||||||||||||||||||

| B | RW |

ENDRX |

Write '1' to enable interrupt for event ENDRX |

||||||||||||||||||||||||||||||||

|

Set |

1 |

Enable |

|||||||||||||||||||||||||||||||||

|

Disabled |

0 |

Read: Disabled |

|||||||||||||||||||||||||||||||||

|

Enabled |

1 |

Read: Enabled |

|||||||||||||||||||||||||||||||||

| C | RW |

END |

Write '1' to enable interrupt for event END |

||||||||||||||||||||||||||||||||

|

Set |

1 |

Enable |

|||||||||||||||||||||||||||||||||

|

Disabled |

0 |

Read: Disabled |

|||||||||||||||||||||||||||||||||

|

Enabled |

1 |

Read: Enabled |

|||||||||||||||||||||||||||||||||

| D | RW |

ENDTX |

Write '1' to enable interrupt for event ENDTX |

||||||||||||||||||||||||||||||||

|

Set |

1 |

Enable |

|||||||||||||||||||||||||||||||||

|

Disabled |

0 |

Read: Disabled |

|||||||||||||||||||||||||||||||||

|

Enabled |

1 |

Read: Enabled |

|||||||||||||||||||||||||||||||||

| E | RW |

STARTED |

Write '1' to enable interrupt for event STARTED |

||||||||||||||||||||||||||||||||

|

Set |

1 |

Enable |

|||||||||||||||||||||||||||||||||

|

Disabled |

0 |

Read: Disabled |

|||||||||||||||||||||||||||||||||

|

Enabled |

1 |

Read: Enabled |

|||||||||||||||||||||||||||||||||

INTENCLR

Address offset: 0x308

Disable interrupt

| Bit number | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ID | E | D | C | B | A | ||||||||||||||||||||||||||||||

| Reset 0x00000000 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| ID | R/W | Field | Value ID | Value | Description | ||||||||||||||||||||||||||||||

| A | RW |

STOPPED |

Write '1' to disable interrupt for event STOPPED |

||||||||||||||||||||||||||||||||

|

Clear |

1 |

Disable |

|||||||||||||||||||||||||||||||||

|

Disabled |

0 |

Read: Disabled |

|||||||||||||||||||||||||||||||||

|

Enabled |

1 |

Read: Enabled |

|||||||||||||||||||||||||||||||||

| B | RW |

ENDRX |

Write '1' to disable interrupt for event ENDRX |

||||||||||||||||||||||||||||||||

|

Clear |

1 |

Disable |

|||||||||||||||||||||||||||||||||

|

Disabled |

0 |

Read: Disabled |

|||||||||||||||||||||||||||||||||

|

Enabled |

1 |

Read: Enabled |

|||||||||||||||||||||||||||||||||

| C | RW |

END |

Write '1' to disable interrupt for event END |

||||||||||||||||||||||||||||||||

|

Clear |

1 |

Disable |

|||||||||||||||||||||||||||||||||

|

Disabled |

0 |

Read: Disabled |

|||||||||||||||||||||||||||||||||

|

Enabled |

1 |

Read: Enabled |

|||||||||||||||||||||||||||||||||

| D | RW |

ENDTX |

Write '1' to disable interrupt for event ENDTX |

||||||||||||||||||||||||||||||||

|

Clear |

1 |

Disable |

|||||||||||||||||||||||||||||||||

|

Disabled |

0 |

Read: Disabled |

|||||||||||||||||||||||||||||||||

|

Enabled |

1 |

Read: Enabled |

|||||||||||||||||||||||||||||||||

| E | RW |

STARTED |

Write '1' to disable interrupt for event STARTED |

||||||||||||||||||||||||||||||||

|

Clear |

1 |

Disable |

|||||||||||||||||||||||||||||||||

|

Disabled |

0 |

Read: Disabled |

|||||||||||||||||||||||||||||||||

|

Enabled |

1 |

Read: Enabled |

|||||||||||||||||||||||||||||||||

STALLSTAT

Address offset: 0x400

Stall status for EasyDMA RAM accesses. The fields in this register are set to STALL by hardware whenever a stall occurres and can be cleared (set to NOSTALL) by the CPU.

| Bit number | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ID | B | A | |||||||||||||||||||||||||||||||||

| Reset 0x00000000 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| ID | R/W | Field | Value ID | Value | Description | ||||||||||||||||||||||||||||||

| A | RW |

TX |

[1..0] |

Stall status for EasyDMA RAM reads |

|||||||||||||||||||||||||||||||

|

NOSTALL |

0 |

No stall |

|||||||||||||||||||||||||||||||||

|

STALL |

1 |

A stall has occurred |

|||||||||||||||||||||||||||||||||

| B | RW |

RX |

[1..0] |

Stall status for EasyDMA RAM writes |

|||||||||||||||||||||||||||||||

|

NOSTALL |

0 |

No stall |

|||||||||||||||||||||||||||||||||

|

STALL |

1 |

A stall has occurred |

|||||||||||||||||||||||||||||||||

ENABLE

Address offset: 0x500

Enable SPIM

| Bit number | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ID | A | A | A | A | |||||||||||||||||||||||||||||||

| Reset 0x00000000 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| ID | R/W | Field | Value ID | Value | Description | ||||||||||||||||||||||||||||||

| A | RW |

ENABLE |

Enable or disable SPIM |

||||||||||||||||||||||||||||||||

|

Disabled |

0 |

Disable SPIM |

|||||||||||||||||||||||||||||||||

|

Enabled |

7 |

Enable SPIM |

|||||||||||||||||||||||||||||||||

PSEL.SCK

Address offset: 0x508

Pin select for SCK

| Bit number | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ID | C |

B |

A | A | A | A | A | ||||||||||||||||||||||||||||

| Reset 0xFFFFFFFF | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | |||

| ID | R/W | Field | Value ID | Value | Description | ||||||||||||||||||||||||||||||

| A | RW |

PIN |

[0..31] |

Pin number |

|||||||||||||||||||||||||||||||

| B | RW |

PORT |

[0..1] |

Port number |

|||||||||||||||||||||||||||||||

| C | RW |

CONNECT |

Connection |

||||||||||||||||||||||||||||||||

|

Disconnected |

1 |

Disconnect |

|||||||||||||||||||||||||||||||||

|

Connected |

0 |

Connect |

|||||||||||||||||||||||||||||||||

PSEL.MOSI

Address offset: 0x50C

Pin select for MOSI signal

| Bit number | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ID | C |

B |

A | A | A | A | A | ||||||||||||||||||||||||||||

| Reset 0xFFFFFFFF | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | |||

| ID | R/W | Field | Value ID | Value | Description | ||||||||||||||||||||||||||||||

| A | RW |

PIN |

[0..31] |

Pin number |

|||||||||||||||||||||||||||||||

| B | RW |

PORT |

[0..1] |

Port number |

|||||||||||||||||||||||||||||||

| C | RW |

CONNECT |

Connection |

||||||||||||||||||||||||||||||||

|

Disconnected |

1 |

Disconnect |

|||||||||||||||||||||||||||||||||

|

Connected |

0 |

Connect |

|||||||||||||||||||||||||||||||||

PSEL.MISO

Address offset: 0x510

Pin select for MISO signal

| Bit number | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ID | C |

B |

A | A | A | A | A | ||||||||||||||||||||||||||||

| Reset 0xFFFFFFFF | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | |||

| ID | R/W | Field | Value ID | Value | Description | ||||||||||||||||||||||||||||||

| A | RW |

PIN |

[0..31] |

Pin number |

|||||||||||||||||||||||||||||||

| B | RW |

PORT |

[0..1] |

Port number |

|||||||||||||||||||||||||||||||

| C | RW |

CONNECT |

Connection |

||||||||||||||||||||||||||||||||

|

Disconnected |

1 |

Disconnect |

|||||||||||||||||||||||||||||||||

|

Connected |

0 |

Connect |

|||||||||||||||||||||||||||||||||

PSEL.CSN

Address offset: 0x514

Pin select for CSN

| Bit number | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ID | C |

B |

A | A | A | A | A | ||||||||||||||||||||||||||||

| Reset 0xFFFFFFFF | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | |||

| ID | R/W | Field | Value ID | Value | Description | ||||||||||||||||||||||||||||||

| A | RW |

PIN |

[0..31] |

Pin number |

|||||||||||||||||||||||||||||||

| B | RW |

PORT |

[0..1] |

Port number |

|||||||||||||||||||||||||||||||

| C | RW |

CONNECT |

Connection |

||||||||||||||||||||||||||||||||

|

Disconnected |

1 |

Disconnect |

|||||||||||||||||||||||||||||||||

|

Connected |

0 |

Connect |

|||||||||||||||||||||||||||||||||

FREQUENCY

Address offset: 0x524

SPI frequency. Accuracy depends on the HFCLK source selected.

| Bit number | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ID | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | |||

| Reset 0x04000000 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| ID | R/W | Field | Value ID | Value | Description | ||||||||||||||||||||||||||||||

| A | RW |

FREQUENCY |

SPI master data rate |

||||||||||||||||||||||||||||||||

|

K125 |

0x02000000 |

125 kbps |

|||||||||||||||||||||||||||||||||

|

K250 |

0x04000000 |

250 kbps |

|||||||||||||||||||||||||||||||||

|

K500 |

0x08000000 |

500 kbps |

|||||||||||||||||||||||||||||||||

|

M1 |

0x10000000 |

1 Mbps |

|||||||||||||||||||||||||||||||||

|

M2 |

0x20000000 |

2 Mbps |

|||||||||||||||||||||||||||||||||

|

M4 |

0x40000000 |

4 Mbps |

|||||||||||||||||||||||||||||||||

|

M8 |

0x80000000 |

8 Mbps |

|||||||||||||||||||||||||||||||||

|

M16 |

0x0A000000 |

16 Mbps |

|||||||||||||||||||||||||||||||||

|

M32 |

0x14000000 |

32 Mbps |

|||||||||||||||||||||||||||||||||

RXD.PTR

Address offset: 0x534

Data pointer

| Bit number | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ID | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | |||

| Reset 0x00000000 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| ID | R/W | Field | Value ID | Value | Description | ||||||||||||||||||||||||||||||

| A | RW |

PTR |

Data pointer See the Memory chapter for details about which memories are available for EasyDMA. |

||||||||||||||||||||||||||||||||

RXD.MAXCNT

Address offset: 0x538

Maximum number of bytes in receive buffer

| Bit number | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ID | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | |||||||||||||||||||

| Reset 0x00000000 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| ID | R/W | Field | Value ID | Value | Description | ||||||||||||||||||||||||||||||

| A | RW |

MAXCNT |

[1..0xFFFF] |

Maximum number of bytes in receive buffer |

|||||||||||||||||||||||||||||||

RXD.AMOUNT

Address offset: 0x53C

Number of bytes transferred in the last transaction

| Bit number | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ID | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | |||||||||||||||||||

| Reset 0x00000000 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| ID | R/W | Field | Value ID | Value | Description | ||||||||||||||||||||||||||||||

| A | R |

AMOUNT |

[1..0xFFFF] |

Number of bytes transferred in the last transaction |

|||||||||||||||||||||||||||||||

RXD.LIST

Address offset: 0x540

EasyDMA list type

| Bit number | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ID | A | A | |||||||||||||||||||||||||||||||||

| Reset 0x00000000 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| ID | R/W | Field | Value ID | Value | Description | ||||||||||||||||||||||||||||||

| A | RW |

LIST |

List type |

||||||||||||||||||||||||||||||||

|

Disabled |

0 |

Disable EasyDMA list |

|||||||||||||||||||||||||||||||||

|

ArrayList |

1 |

Use array list |

|||||||||||||||||||||||||||||||||

TXD.PTR

Address offset: 0x544

Data pointer

| Bit number | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ID | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | |||

| Reset 0x00000000 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| ID | R/W | Field | Value ID | Value | Description | ||||||||||||||||||||||||||||||

| A | RW |

PTR |

Data pointer See the Memory chapter for details about which memories are available for EasyDMA. |

||||||||||||||||||||||||||||||||

TXD.MAXCNT

Address offset: 0x548

Number of bytes in transmit buffer

| Bit number | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ID | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | |||||||||||||||||||

| Reset 0x00000000 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| ID | R/W | Field | Value ID | Value | Description | ||||||||||||||||||||||||||||||

| A | RW |

MAXCNT |

[1..0xFFFF] |

Maximum number of bytes in transmit buffer |

|||||||||||||||||||||||||||||||

TXD.AMOUNT

Address offset: 0x54C

Number of bytes transferred in the last transaction

| Bit number | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ID | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | A | |||||||||||||||||||

| Reset 0x00000000 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| ID | R/W | Field | Value ID | Value | Description | ||||||||||||||||||||||||||||||

| A | R |

AMOUNT |

[1..0xFFFF] |

Number of bytes transferred in the last transaction |

|||||||||||||||||||||||||||||||

TXD.LIST

Address offset: 0x550

EasyDMA list type

| Bit number | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ID | A | A | |||||||||||||||||||||||||||||||||

| Reset 0x00000000 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| ID | R/W | Field | Value ID | Value | Description | ||||||||||||||||||||||||||||||

| A | RW |

LIST |

List type |

||||||||||||||||||||||||||||||||

|

Disabled |

0 |

Disable EasyDMA list |

|||||||||||||||||||||||||||||||||

|

ArrayList |

1 |

Use array list |

|||||||||||||||||||||||||||||||||

CONFIG

Address offset: 0x554

Configuration register

| Bit number | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ID | C | B | A | ||||||||||||||||||||||||||||||||

| Reset 0x00000000 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| ID | R/W | Field | Value ID | Value | Description | ||||||||||||||||||||||||||||||

| A | RW |

ORDER |

Bit order |

||||||||||||||||||||||||||||||||

|

MsbFirst |

0 |

Most significant bit shifted out first |

|||||||||||||||||||||||||||||||||

|

LsbFirst |

1 |

Least significant bit shifted out first |

|||||||||||||||||||||||||||||||||

| B | RW |

CPHA |

Serial clock (SCK) phase |

||||||||||||||||||||||||||||||||

|

Leading |

0 |

Sample on leading edge of clock, shift serial data on trailing edge |

|||||||||||||||||||||||||||||||||

|

Trailing |

1 |

Sample on trailing edge of clock, shift serial data on leading edge |

|||||||||||||||||||||||||||||||||

| C | RW |

CPOL |

Serial clock (SCK) polarity |

||||||||||||||||||||||||||||||||

|

ActiveHigh |

0 |

Active high |

|||||||||||||||||||||||||||||||||

|

ActiveLow |

1 |

Active low |

|||||||||||||||||||||||||||||||||

IFTIMING.RXDELAY

Address offset: 0x560

Sample delay for input serial data on MISO

| Bit number | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ID | A | A | A | ||||||||||||||||||||||||||||||||

| Reset 0x00000002 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | |||

| ID | R/W | Field | Value ID | Value | Description | ||||||||||||||||||||||||||||||

| A | RW |

RXDELAY |

[7..0] |

Sample delay for input serial data on MISO. The value specifies the number of 64 MHz clock cycles (15.625 ns) delay from the the sampling edge of SCK (leading edge for CONFIG.CPHA = 0, trailing edge for CONFIG.CPHA = 1) until the input serial data is sampled. As en example, if RXDELAY = 0 and CONFIG.CPHA = 0, the input serial data is sampled on the rising edge of SCK. |

|||||||||||||||||||||||||||||||

IFTIMING.CSNDUR

Address offset: 0x564

Minimum duration between edge of CSN and edge of SCK. When SHORTS.END_START is used, this is also the minimum duration CSN must stay high between transactions.

| Bit number | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ID | A | A | A | A | A | A | A | A | |||||||||||||||||||||||||||

| Reset 0x00000002 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | |||

| ID | R/W | Field | Value ID | Value | Description | ||||||||||||||||||||||||||||||

| A | RW |

CSNDUR |

[0xFF..0] |

Minimum duration between edge of CSN and edge of SCK. When SHORTS.END_START is used, this is the minimum duration CSN must stay high between transactions. The value is specified in number of 64 MHz clock cycles (15.625 ns). Note that for low values of CSNDUR, the system turnaround time will dominate the actual time between transactions. |

|||||||||||||||||||||||||||||||

CSNPOL

Address offset: 0x568

Polarity of CSN output

| Bit number | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ID | A | ||||||||||||||||||||||||||||||||||

| Reset 0x00000000 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| ID | R/W | Field | Value ID | Value | Description | ||||||||||||||||||||||||||||||

| A | RW |

CSNPOL |

Polarity of CSN output |

||||||||||||||||||||||||||||||||

|

LOW |

0 |

Active low (idle state high) |

|||||||||||||||||||||||||||||||||

|

HIGH |

1 |

Active high (idle state low) |

|||||||||||||||||||||||||||||||||

PSELDCX

Address offset: 0x56C

Pin select for DCX signal

| Bit number | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ID | C |

B |

A | A | A | A | A | ||||||||||||||||||||||||||||

| Reset 0xFFFFFFFF | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | |||

| ID | R/W | Field | Value ID | Value | Description | ||||||||||||||||||||||||||||||

| A | RW |

PIN |

[0..31] |

Pin number |

|||||||||||||||||||||||||||||||

| B | RW |

PORT |

[0..1] |

Port number |

|||||||||||||||||||||||||||||||

| C | RW |

CONNECT |

Connection |

||||||||||||||||||||||||||||||||

|

Disconnected |

1 |

Disconnect |

|||||||||||||||||||||||||||||||||

|

Connected |

0 |

Connect |

|||||||||||||||||||||||||||||||||

DCXCNT

Address offset: 0x570

DCX configuration

| Bit number | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ID | A | A | A | A | |||||||||||||||||||||||||||||||

| Reset 0x00000000 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| ID | R/W | Field | Value ID | Value | Description | ||||||||||||||||||||||||||||||

| A | RW |

DCXCNT |

0x0..0xF |

This register specifies the number of command bytes preceding the data bytes. The PSEL.DCX line will be low during transmission of command bytes and high during transmission of data bytes. Value 0xF indicates that all bytes are command bytes. |

|||||||||||||||||||||||||||||||

ORC

Address offset: 0x5C0

Byte transmitted after TXD.MAXCNT bytes have been transmitted in the case when RXD.MAXCNT is greater than TXD.MAXCNT

| Bit number | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ID | A | A | A | A | A | A | A | A | |||||||||||||||||||||||||||

| Reset 0x00000000 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| ID | R/W | Field | Value ID | Value | Description | ||||||||||||||||||||||||||||||

| A | RW |

ORC |

Byte transmitted after TXD.MAXCNT bytes have been transmitted in the case when RXD.MAXCNT is greater than TXD.MAXCNT. |

||||||||||||||||||||||||||||||||

Electrical specification

Timing specifications

| Symbol | Description | Min. | Typ. | Max. | Units | ||||

|---|---|---|---|---|---|---|---|---|---|

| fSPIM |

Bit rates for SPIM1 |

162 | Mbps | ||||||

| tSPIM,START |

Time from START task to transmission started |

1 | µs | ||||||

| tSPIM,CSCK |

SCK period |

125 | ns | ||||||

| tSPIM,RSCK,LD |

SCK rise time, standard drivea |

tRF,25pF | |||||||

| tSPIM,RSCK,HD |

SCK rise time, high drivea |

tHRF,25pF | |||||||

| tSPIM,FSCK,LD |

SCK fall time, standard drivea |

tRF,25pF | |||||||

| tSPIM,FSCK,HD |

SCK fall time, high drivea |

tHRF,25pF | |||||||

| tSPIM,WHSCK |

SCK high timea |

(tCSCK/2) - tRSCK - 1.5 ns | |||||||

| tSPIM,WLSCK |

SCK low timea |

(tCSCK/2) - tFSCK - 1.5 ns | |||||||

| tSPIM,SUMI |

MISO to CLK edge setup time |

19 | ns | ||||||

| tSPIM,HMI |

CLK edge to MISO hold time |

10 | ns | ||||||

| tSPIM,VMO |

CLK edge to MOSI valid, SCK frequency ≤ 8 MHz |

59 | ns | ||||||

| tSPIM,VMO,HS |

CLK edge to MOSI valid, SCK frequency > 8 MHz |

.. | .. | .. | ns | ||||

| tSPIM,HMO |

MOSI hold time after CLK edge |

10 | ns |