CLOCK — Clock control

The clock control system can source the system clocks from a range of internal or external high and low frequency oscillators and distribute them to modules based upon a module’s individual requirements. Clock distribution is automated and grouped independently by module to limit current consumption in unused branches of the clock tree.

Listed here are the main features for CLOCK:

- 64 MHz on-chip oscillator

- 64 MHz crystal oscillator, using external 32 MHz crystal

- 32.768 kHz +/-500 ppm RC oscillator

- 32.768 kHz crystal oscillator, using external 32.768 kHz crystal

- 32.768 kHz oscillator synthesized from 64 MHz oscillator

- Firmware (FW) override control of oscillator activity for low latency start up

- Automatic oscillator and clock control, and distribution for ultra-low power

HFCLK clock controller

The HFCLK clock controller provides the following clocks to the system.

- HCLK64M: 64 MHz CPU clock

- PCLK1M: 1 MHz peripheral clock

- PCLK16M: 16 MHz peripheral clock

- PCLK32M: 32 MHz peripheral clock

The HFCLK controller supports the following high frequency clock (HFCLK) sources:

- 64 MHz internal oscillator (HFINT)

- 64 MHz crystal oscillator (HFXO)

For illustration, see Clock control.

When the system requests one or more clocks from the HFCLK controller, the HFCLK controller will automatically provide them. If the system does not request any clocks provided by the HFCLK controller, the controller will enter a power saving mode.

These clocks are only available when the system is in ON mode. When the system enters ON mode, the internal oscillator (HFINT) clock source will automatically start to be able to provide the required HFCLK clock(s) for the system.

The HFINT will be used when HFCLK is requested and HFXO has not been started. The HFXO is started by triggering the HFCLKSTART task and stopped using the HFCLKSTOP task. A HFCLKSTARTED event will be generated when the HFXO has started and its frequency is stable.

The HFXO must be running to use the RADIO or the calibration mechanism associated with the 32.768 kHz RC oscillator.

64 MHz crystal oscillator (HFXO)

The 64 MHz crystal oscillator (HFXO) is controlled by a 32 MHz external crystal

The crystal oscillator is designed for use with an AT-cut quartz crystal in parallel resonant mode. To achieve correct oscillation frequency, the load capacitance must match the specification in the crystal data sheet.

Circuit diagram of the 64 MHz crystal oscillator shows how the 32 MHz crystal is connected to the 64 MHz crystal oscillator.

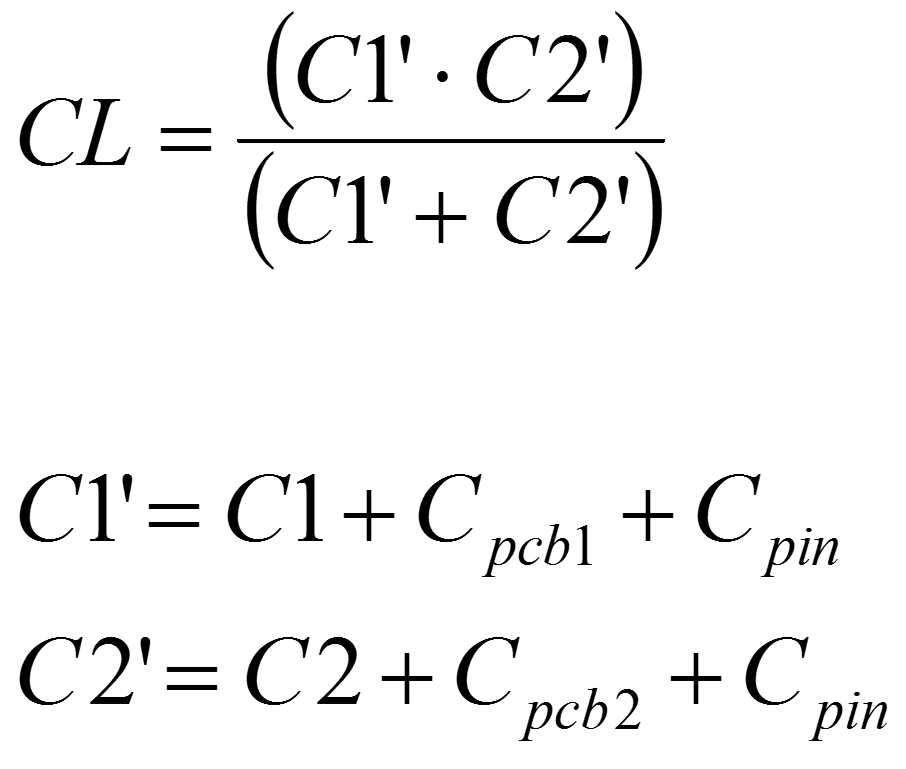

The load capacitance (CL) is the total capacitance seen by the crystal across its terminals and is given by:

C1 and C2 are ceramic SMD capacitors connected between each crystal terminal and ground. For

more information, see Reference circuitry.

Cpcb1 and Cpcb2 are stray capacitances on the PCB. Cpin is the

pin input capacitance on the XC1 and XC2 pins. See table 64 MHz crystal oscillator (HFXO). The load capacitors C1

and C2 should have the same value.

For reliable operation, the crystal load capacitance, shunt capacitance, equivalent series resistance, and drive level must comply with the specifications in table 64 MHz crystal oscillator (HFXO). It is recommended to use a crystal with lower than maximum load capacitance and/or shunt capacitance. A low load capacitance will reduce both start up time and current consumption.

LFCLK clock controller

The system supports several low frequency clock sources.

As illustrated in Clock control, the system supports the following low frequency clock sources:

- 32.768 kHz RC oscillator (LFRC)

- 32.768 kHz crystal oscillator (LFXO)

- 32.768 kHz synthesized from HFCLK (LFSYNT)

The LFCLK clock is started by first selecting the preferred clock source in register LFCLKSRC and then triggering the LFCLKSTART task. If the LFXO is selected as the clock source, the LFCLK will initially start running from the 32.768 kHz LFRC while the LFXO is starting up and automatically switch to using the LFXO once this oscillator is running. The LFCLKSTARTED event will be generated when the LFXO has been started.

The LFCLK clock is stopped by triggering the LFCLKSTOP task.

It is not allowed to write to register LFCLKSRC when the LFCLK is running.

A LFCLKSTOP task will stop the LFCLK oscillator. However, the LFCLKSTOP task can only be triggered after the STATE field in register LFCLKSTAT indicates a 'LFCLK running' state.

The LFCLK clock controller and all of the LFCLK clock sources are always switched off when in OFF mode.

32.768 kHz RC oscillator (LFRC)

The default source of the low frequency clock (LFCLK) is the 32.768 kHz RC oscillator (LFRC).

The LFRC frequency will be affected by variation in temperature. The LFRC oscillator can be calibrated to improve accuracy by using the HFXO as a reference oscillator during calibration. See Table 32.768 kHz RC oscillator (LFRC) for details on the default and calibrated accuracy of the LFRC oscillator. The LFRC oscillator does not require additional external components.

Calibrating the 32.768 kHz RC oscillator

After the 32.768 kHz RC oscillator is started and running, it can be calibrated by triggering the CAL task. In this case, the HFCLK will be temporarily switched on and used as a reference.

A DONE event will be generated when calibration has finished. The calibration mechanism will only work as long as HFCLK is generated from the HFCLK crystal oscillator, it is therefore necessary to explicitly start this crystal oscillator before calibration can be started, see HFCLKSTART task.

It is not allowed to stop the LFRC during an ongoing calibration.

Calibration timer

The calibration timer can be used to time the calibration interval of the 32.768 kHz RC oscillator.

The calibration timer is started by triggering the CTSTART task and stopped by triggering the CTSTOP task. The calibration timer will always start counting down from the value specified in CTIV and generate a CTTO timeout event when it reaches 0. The Calibration timer will stop by itself when it reaches 0.

Due to limitations in the calibration timer, only one task related to calibration, that is, CAL, CTSTART and CTSTOP, can be triggered for every period of LFCLK.

32.768 kHz crystal oscillator (LFXO)

For higher LFCLK accuracy the low frequency crystal oscillator (LFXO) must be used.

The following external clock sources are supported:

- Low swing clock signal applied to the XL1 pin. The XL2 pin shall then be grounded.

- Rail-to-rail clock signal applied to the XL1 pin. The XL2 pin shall then be grounded or left unconnected.

The LFCLKSRC register controls the clock source, and its allowed swing. The truth table for various situations is as follows:

| SRC | EXTERNAL | BYPASS | Comment |

|---|---|---|---|

| 0 | 0 | 0 | Normal operation, RC is source |

| 0 | 0 | 1 | DO NOT USE |

| 0 | 1 | X | DO NOT USE |

| 1 | 0 | 0 | Normal XTAL operation |

| 1 | 1 | 0 | Apply external low swing signal to XL1, ground XL2 |

| 1 | 1 | 1 | Apply external full swing signal to XL1, leave XL2 grounded or unconnected |

| 1 | 0 | 1 | DO NOT USE |

| 2 | 0 | 0 | Normal operation, synth is source |

| 2 | 0 | 1 | DO NOT USE |

| 2 | 1 | X | DO NOT USE |

To achieve correct oscillation frequency, the load capacitance must match the specification in the crystal data sheet. Circuit diagram of the 32.768 kHz crystal oscillator shows the LFXO circuitry.

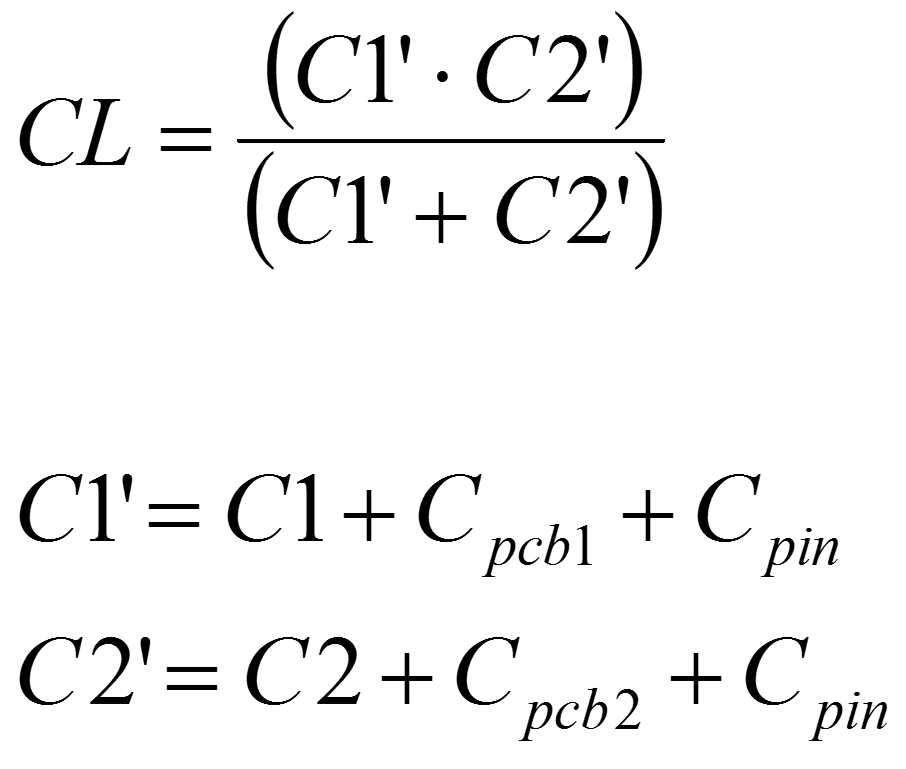

The load capacitance (CL) is the total capacitance seen by the crystal across its terminals and is given by:

C1 and C2 are ceramic SMD capacitors connected between each crystal terminal and ground. Cpcb1 and Cpcb2 are stray capacitances on the PCB. Cpin is the pin input capacitance on the XC1 and XC2 pins (see 32.768 kHz crystal oscillator (LFXO)). The load capacitors C1 and C2 should have the same value.

For more information, see Reference circuitry.

32.768 kHz synthesized from HFCLK (LFSYNT)

LFCLK can also be synthesized from the HFCLK clock source. The accuracy of LFCLK will then be the accuracy of the HFCLK.

Using the LFSYNT clock avoids the requirement for a 32.768 kHz crystal, but increases average power consumption as the HFCLK will need to be requested in the system.

Registers

| Base address | Peripheral | Instance | Description | Configuration | |

|---|---|---|---|---|---|

| 0x40000000 | CLOCK | CLOCK |

Clock control |

||

| Register | Offset | Description | |

|---|---|---|---|

| TASKS_HFCLKSTART | 0x000 |

Start HFCLK crystal oscillator |

|

| TASKS_HFCLKSTOP | 0x004 |

Stop HFCLK crystal oscillator |

|

| TASKS_LFCLKSTART | 0x008 |

Start LFCLK source |

|

| TASKS_LFCLKSTOP | 0x00C |

Stop LFCLK source |

|

| TASKS_CAL | 0x010 |

Start calibration of LFRC oscillator |

|

| TASKS_CTSTART | 0x014 |

Start calibration timer |

|

| TASKS_CTSTOP | 0x018 |

Stop calibration timer |

|

| EVENTS_HFCLKSTARTED | 0x100 |

HFCLK oscillator started |

|

| EVENTS_LFCLKSTARTED | 0x104 |

LFCLK started |

|

| EVENTS_DONE | 0x10C |

Calibration of LFCLK RC oscillator complete event |

|

| EVENTS_CTTO | 0x110 |

Calibration timer timeout |

|

| INTENSET | 0x304 |

Enable interrupt |

|

| INTENCLR | 0x308 |

Disable interrupt |

|

| HFCLKRUN | 0x408 |

Status indicating that HFCLKSTART task has been triggered |

|

| HFCLKSTAT | 0x40C |

HFCLK status |

|

| LFCLKRUN | 0x414 |

Status indicating that LFCLKSTART task has been triggered |

|

| LFCLKSTAT | 0x418 |

LFCLK status |

|

| LFCLKSRCCOPY | 0x41C |

Copy of LFCLKSRC register, set when LFCLKSTART task was triggered |

|

| LFCLKSRC | 0x518 |

Clock source for the LFCLK |

|

| CTIV | 0x538 |

Calibration timer interval |

Retained |

TASKS_HFCLKSTART

Address offset: 0x000

Start HFCLK crystal oscillator

| Bit number | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ID | A | ||||||||||||||||||||||||||||||||||

| Reset 0x00000000 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| ID | Access | Field | Value ID | Value | Description | ||||||||||||||||||||||||||||||

| A | W |

TASKS_HFCLKSTART |

Start HFCLK crystal oscillator |

||||||||||||||||||||||||||||||||

|

Trigger |

1 |

Trigger task |

|||||||||||||||||||||||||||||||||

TASKS_HFCLKSTOP

Address offset: 0x004

Stop HFCLK crystal oscillator

| Bit number | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ID | A | ||||||||||||||||||||||||||||||||||

| Reset 0x00000000 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| ID | Access | Field | Value ID | Value | Description | ||||||||||||||||||||||||||||||

| A | W |

TASKS_HFCLKSTOP |

Stop HFCLK crystal oscillator |

||||||||||||||||||||||||||||||||

|

Trigger |

1 |

Trigger task |

|||||||||||||||||||||||||||||||||

TASKS_LFCLKSTART

Address offset: 0x008

Start LFCLK source

| Bit number | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ID | A | ||||||||||||||||||||||||||||||||||

| Reset 0x00000000 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| ID | Access | Field | Value ID | Value | Description | ||||||||||||||||||||||||||||||

| A | W |

TASKS_LFCLKSTART |

Start LFCLK source |

||||||||||||||||||||||||||||||||

|

Trigger |

1 |

Trigger task |

|||||||||||||||||||||||||||||||||

TASKS_LFCLKSTOP

Address offset: 0x00C

Stop LFCLK source

| Bit number | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ID | A | ||||||||||||||||||||||||||||||||||

| Reset 0x00000000 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| ID | Access | Field | Value ID | Value | Description | ||||||||||||||||||||||||||||||

| A | W |

TASKS_LFCLKSTOP |

Stop LFCLK source |

||||||||||||||||||||||||||||||||

|

Trigger |

1 |

Trigger task |

|||||||||||||||||||||||||||||||||

TASKS_CAL

Address offset: 0x010

Start calibration of LFRC oscillator

| Bit number | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ID | A | ||||||||||||||||||||||||||||||||||

| Reset 0x00000000 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| ID | Access | Field | Value ID | Value | Description | ||||||||||||||||||||||||||||||

| A | W |

TASKS_CAL |

Start calibration of LFRC oscillator |

||||||||||||||||||||||||||||||||

|

Trigger |

1 |

Trigger task |

|||||||||||||||||||||||||||||||||

TASKS_CTSTART

Address offset: 0x014

Start calibration timer

| Bit number | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ID | A | ||||||||||||||||||||||||||||||||||

| Reset 0x00000000 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| ID | Access | Field | Value ID | Value | Description | ||||||||||||||||||||||||||||||

| A | W |

TASKS_CTSTART |

Start calibration timer |

||||||||||||||||||||||||||||||||

|

Trigger |

1 |

Trigger task |

|||||||||||||||||||||||||||||||||

TASKS_CTSTOP

Address offset: 0x018

Stop calibration timer

| Bit number | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ID | A | ||||||||||||||||||||||||||||||||||

| Reset 0x00000000 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| ID | Access | Field | Value ID | Value | Description | ||||||||||||||||||||||||||||||

| A | W |

TASKS_CTSTOP |

Stop calibration timer |

||||||||||||||||||||||||||||||||

|

Trigger |

1 |

Trigger task |

|||||||||||||||||||||||||||||||||

EVENTS_HFCLKSTARTED

Address offset: 0x100

HFCLK oscillator started

| Bit number | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ID | A | ||||||||||||||||||||||||||||||||||

| Reset 0x00000000 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| ID | Access | Field | Value ID | Value | Description | ||||||||||||||||||||||||||||||

| A | RW |

EVENTS_HFCLKSTARTED |

HFCLK oscillator started |

||||||||||||||||||||||||||||||||

|

NotGenerated |

0 |

Event not generated |

|||||||||||||||||||||||||||||||||

|

Generated |

1 |

Event generated |

|||||||||||||||||||||||||||||||||

EVENTS_LFCLKSTARTED

Address offset: 0x104

LFCLK started

| Bit number | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ID | A | ||||||||||||||||||||||||||||||||||

| Reset 0x00000000 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| ID | Access | Field | Value ID | Value | Description | ||||||||||||||||||||||||||||||

| A | RW |

EVENTS_LFCLKSTARTED |

LFCLK started |

||||||||||||||||||||||||||||||||

|

NotGenerated |

0 |

Event not generated |

|||||||||||||||||||||||||||||||||

|

Generated |

1 |

Event generated |

|||||||||||||||||||||||||||||||||

EVENTS_DONE

Address offset: 0x10C

Calibration of LFCLK RC oscillator complete event

| Bit number | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ID | A | ||||||||||||||||||||||||||||||||||

| Reset 0x00000000 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| ID | Access | Field | Value ID | Value | Description | ||||||||||||||||||||||||||||||

| A | RW |

EVENTS_DONE |

Calibration of LFCLK RC oscillator complete event |

||||||||||||||||||||||||||||||||

|

NotGenerated |

0 |

Event not generated |

|||||||||||||||||||||||||||||||||

|

Generated |

1 |

Event generated |

|||||||||||||||||||||||||||||||||

EVENTS_CTTO

Address offset: 0x110

Calibration timer timeout

| Bit number | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ID | A | ||||||||||||||||||||||||||||||||||

| Reset 0x00000000 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| ID | Access | Field | Value ID | Value | Description | ||||||||||||||||||||||||||||||

| A | RW |

EVENTS_CTTO |

Calibration timer timeout |

||||||||||||||||||||||||||||||||

|

NotGenerated |

0 |

Event not generated |

|||||||||||||||||||||||||||||||||

|

Generated |

1 |

Event generated |

|||||||||||||||||||||||||||||||||

INTENSET

Address offset: 0x304

Enable interrupt

| Bit number | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ID | D | C | B | A | |||||||||||||||||||||||||||||||

| Reset 0x00000000 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| ID | Access | Field | Value ID | Value | Description | ||||||||||||||||||||||||||||||

| A | RW |

HFCLKSTARTED |

Write '1' to enable interrupt for event HFCLKSTARTED |

||||||||||||||||||||||||||||||||

|

Set |

1 |

Enable |

|||||||||||||||||||||||||||||||||

|

Disabled |

0 |

Read: Disabled |

|||||||||||||||||||||||||||||||||

|

Enabled |

1 |

Read: Enabled |

|||||||||||||||||||||||||||||||||

| B | RW |

LFCLKSTARTED |

Write '1' to enable interrupt for event LFCLKSTARTED |

||||||||||||||||||||||||||||||||

|

Set |

1 |

Enable |

|||||||||||||||||||||||||||||||||

|

Disabled |

0 |

Read: Disabled |

|||||||||||||||||||||||||||||||||

|

Enabled |

1 |

Read: Enabled |

|||||||||||||||||||||||||||||||||

| C | RW |

DONE |

Write '1' to enable interrupt for event DONE |

||||||||||||||||||||||||||||||||

|

Set |

1 |

Enable |

|||||||||||||||||||||||||||||||||

|

Disabled |

0 |

Read: Disabled |

|||||||||||||||||||||||||||||||||

|

Enabled |

1 |

Read: Enabled |

|||||||||||||||||||||||||||||||||

| D | RW |

CTTO |

Write '1' to enable interrupt for event CTTO |

||||||||||||||||||||||||||||||||

|

Set |

1 |

Enable |

|||||||||||||||||||||||||||||||||

|

Disabled |

0 |

Read: Disabled |

|||||||||||||||||||||||||||||||||

|

Enabled |

1 |

Read: Enabled |

|||||||||||||||||||||||||||||||||

INTENCLR

Address offset: 0x308

Disable interrupt

| Bit number | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ID | D | C | B | A | |||||||||||||||||||||||||||||||

| Reset 0x00000000 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| ID | Access | Field | Value ID | Value | Description | ||||||||||||||||||||||||||||||

| A | RW |

HFCLKSTARTED |

Write '1' to disable interrupt for event HFCLKSTARTED |

||||||||||||||||||||||||||||||||

|

Clear |

1 |

Disable |

|||||||||||||||||||||||||||||||||

|

Disabled |

0 |

Read: Disabled |

|||||||||||||||||||||||||||||||||

|

Enabled |

1 |

Read: Enabled |

|||||||||||||||||||||||||||||||||

| B | RW |

LFCLKSTARTED |

Write '1' to disable interrupt for event LFCLKSTARTED |

||||||||||||||||||||||||||||||||

|

Clear |

1 |

Disable |

|||||||||||||||||||||||||||||||||

|

Disabled |

0 |

Read: Disabled |

|||||||||||||||||||||||||||||||||

|

Enabled |

1 |

Read: Enabled |

|||||||||||||||||||||||||||||||||

| C | RW |

DONE |

Write '1' to disable interrupt for event DONE |

||||||||||||||||||||||||||||||||

|

Clear |

1 |

Disable |

|||||||||||||||||||||||||||||||||

|

Disabled |

0 |

Read: Disabled |

|||||||||||||||||||||||||||||||||

|

Enabled |

1 |

Read: Enabled |

|||||||||||||||||||||||||||||||||

| D | RW |

CTTO |

Write '1' to disable interrupt for event CTTO |

||||||||||||||||||||||||||||||||

|

Clear |

1 |

Disable |

|||||||||||||||||||||||||||||||||

|

Disabled |

0 |

Read: Disabled |

|||||||||||||||||||||||||||||||||

|

Enabled |

1 |

Read: Enabled |

|||||||||||||||||||||||||||||||||

HFCLKRUN

Address offset: 0x408

Status indicating that HFCLKSTART task has been triggered

| Bit number | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ID | A | ||||||||||||||||||||||||||||||||||

| Reset 0x00000000 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| ID | Access | Field | Value ID | Value | Description | ||||||||||||||||||||||||||||||

| A | R |

STATUS |

HFCLKSTART task triggered or not |

||||||||||||||||||||||||||||||||

|

NotTriggered |

0 |

Task not triggered |

|||||||||||||||||||||||||||||||||

|

Triggered |

1 |

Task triggered |

|||||||||||||||||||||||||||||||||

HFCLKSTAT

Address offset: 0x40C

HFCLK status

| Bit number | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ID | B | A | |||||||||||||||||||||||||||||||||

| Reset 0x00000000 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| ID | Access | Field | Value ID | Value | Description | ||||||||||||||||||||||||||||||

| A | R |

SRC |

Source of HFCLK |

||||||||||||||||||||||||||||||||

|

RC |

0 |

64 MHz internal oscillator (HFINT) |

|||||||||||||||||||||||||||||||||

|

Xtal |

1 |

64 MHz crystal oscillator (HFXO) |

|||||||||||||||||||||||||||||||||

| B | R |

STATE |

HFCLK state |

||||||||||||||||||||||||||||||||

|

NotRunning |

0 |

HFCLK not running |

|||||||||||||||||||||||||||||||||

|

Running |

1 |

HFCLK running |

|||||||||||||||||||||||||||||||||

LFCLKRUN

Address offset: 0x414

Status indicating that LFCLKSTART task has been triggered

| Bit number | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ID | A | ||||||||||||||||||||||||||||||||||

| Reset 0x00000000 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| ID | Access | Field | Value ID | Value | Description | ||||||||||||||||||||||||||||||

| A | R |

STATUS |

LFCLKSTART task triggered or not |

||||||||||||||||||||||||||||||||

|

NotTriggered |

0 |

Task not triggered |

|||||||||||||||||||||||||||||||||

|

Triggered |

1 |

Task triggered |

|||||||||||||||||||||||||||||||||

LFCLKSTAT

Address offset: 0x418

LFCLK status

| Bit number | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ID | B | A | A | ||||||||||||||||||||||||||||||||

| Reset 0x00000000 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| ID | Access | Field | Value ID | Value | Description | ||||||||||||||||||||||||||||||

| A | R |

SRC |

Source of LFCLK |

||||||||||||||||||||||||||||||||

|

RC |

0 |

32.768 kHz RC oscillator |

|||||||||||||||||||||||||||||||||

|

Xtal |

1 |

32.768 kHz crystal oscillator |

|||||||||||||||||||||||||||||||||

|

Synth |

2 |

32.768 kHz synthesized from HFCLK |

|||||||||||||||||||||||||||||||||

| B | R |

STATE |

LFCLK state |

||||||||||||||||||||||||||||||||

|

NotRunning |

0 |

LFCLK not running |

|||||||||||||||||||||||||||||||||

|

Running |

1 |

LFCLK running |

|||||||||||||||||||||||||||||||||

LFCLKSRCCOPY

Address offset: 0x41C

Copy of LFCLKSRC register, set when LFCLKSTART task was triggered

| Bit number | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ID | A | A | |||||||||||||||||||||||||||||||||

| Reset 0x00000000 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| ID | Access | Field | Value ID | Value | Description | ||||||||||||||||||||||||||||||

| A | R |

SRC |

Clock source |

||||||||||||||||||||||||||||||||

|

RC |

0 |

32.768 kHz RC oscillator |

|||||||||||||||||||||||||||||||||

|

Xtal |

1 |

32.768 kHz crystal oscillator |

|||||||||||||||||||||||||||||||||

|

Synth |

2 |

32.768 kHz synthesized from HFCLK |

|||||||||||||||||||||||||||||||||

LFCLKSRC

Address offset: 0x518

Clock source for the LFCLK

| Bit number | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ID | C | B | A | A | |||||||||||||||||||||||||||||||

| Reset 0x00000000 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| ID | Access | Field | Value ID | Value | Description | ||||||||||||||||||||||||||||||

| A | RW |

SRC |

Clock source |

||||||||||||||||||||||||||||||||

|

RC |

0 |

32.768 kHz RC oscillator |

|||||||||||||||||||||||||||||||||

|

Xtal |

1 |

32.768 kHz crystal oscillator |

|||||||||||||||||||||||||||||||||

|

Synth |

2 |

32.768 kHz synthesized from HFCLK |

|||||||||||||||||||||||||||||||||

| B | RW |

BYPASS |

Enable or disable bypass of LFCLK crystal oscillator with external clock source |

||||||||||||||||||||||||||||||||

|

Disabled |

0 |

Disable (use with Xtal or low-swing external source) |

|||||||||||||||||||||||||||||||||

|

Enabled |

1 |

Enable (use with rail-to-rail external source) |

|||||||||||||||||||||||||||||||||

| C | RW |

EXTERNAL |

Enable or disable external source for LFCLK |

||||||||||||||||||||||||||||||||

|

Disabled |

0 |

Disable external source (use with Xtal) |

|||||||||||||||||||||||||||||||||

|

Enabled |

1 |

Enable use of external source instead of Xtal (SRC needs to be set to Xtal) |

|||||||||||||||||||||||||||||||||

CTIV ( Retained )

Address offset: 0x538

This register is a retained register

Calibration timer interval

| Bit number | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ID | A | A | A | A | A | A | A | ||||||||||||||||||||||||||||

| Reset 0x00000000 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| ID | Access | Field | Value ID | Value | Description | ||||||||||||||||||||||||||||||

| A | RW |

CTIV |

Calibration timer interval in multiple of 0.25 seconds. Range: 0.25 seconds to 31.75 seconds. |

||||||||||||||||||||||||||||||||

Electrical specification

64 MHz internal oscillator (HFINT)

| Symbol | Description | Min. | Typ. | Max. | Units | ||||

|---|---|---|---|---|---|---|---|---|---|

| fNOM_HFINT |

Nominal output frequency |

64 | MHz | ||||||

| fTOL_HFINT |

Frequency tolerance |

<±1.5 | <±8 | % | |||||

| tSTART_HFINT |

Startup time |

3 | us |

64 MHz crystal oscillator (HFXO)

| Symbol | Description | Min. | Typ. | Max. | Units | ||||

|---|---|---|---|---|---|---|---|---|---|

| fNOM_HFXO |

Nominal output frequency |

64 | MHz | ||||||

| fXTAL_HFXO |

External crystal frequency |

32 | MHz | ||||||

| fTOL_HFXO |

Frequency tolerance requirement for 2.4 GHz proprietary radio applications |

±60 | ppm | ||||||

| fTOL_HFXO_BLE |

Frequency tolerance requirement, Bluetooth low energy applications |

±40 | ppm | ||||||

| CL_HFXO |

Load capacitance |

12 | pF | ||||||

| C0_HFXO |

Shunt capacitance |

7 | pF | ||||||

| RS_HFXO_7PF |

Equivalent series resistance C0 = 7 pF |

60 | ohm | ||||||

| RS_HFXO_5PF |

Equivalent series resistance C0 = 5 pF |

60 | ohm | ||||||

| RS_HFXO_3PF |

Equivalent series resistance C0 = 3 pF |

100 | ohm | ||||||

| PD_HFXO |

Drive level |

100 | uW | ||||||

| CPIN_HFXO |

Input capacitance XC1 and XC2 |

4 | pF | ||||||

| tSTART_HFXO |

Startup time |

0.36 | ms |

32.768 kHz RC oscillator (LFRC)

| Symbol | Description | Min. | Typ. | Max. | Units | ||||

|---|---|---|---|---|---|---|---|---|---|

| fNOM_LFRC |

Nominal frequency |

32.768 | kHz | ||||||

| fTOL_LFRC |

Frequency tolerance |

±2 | % | ||||||

| fTOL_CAL_LFRC |

Frequency tolerance for LFRC after calibration1 |

±500 | ppm | ||||||

| tSTART_LFRC |

Startup time for 32.768 kHz RC oscillator |

600 | us |

32.768 kHz crystal oscillator (LFXO)

| Symbol | Description | Min. | Typ. | Max. | Units | ||||

|---|---|---|---|---|---|---|---|---|---|

| fNOM_LFXO |

Crystal frequency |

32.768 | kHz | ||||||

| fTOL_LFXO_BLE |

Frequency tolerance requirement for BLE stack |

±250 | ppm | ||||||

| fTOL_LFXO_ANT |

Frequency tolerance requirement for ANT stack |

±50 | ppm | ||||||

| CL_LFXO |

Load capacitance |

12.5 | pF | ||||||

| C0_LFXO |

Shunt capacitance |

2 | pF | ||||||

| RS_LFXO |

Equivalent series resistance |

100 | kohm | ||||||

| PD_LFXO |

Drive level |

0.5 | uW | ||||||

| Cpin |

Input capacitance on XL1 and XL2 pads |

4 | pF | ||||||

| tSTART_LFXO |

Startup time for 32.768 kHz crystal oscillator |

0.25 | s | ||||||

| VAMP_IN_XO_LOW |

Peak to peak amplitude for external low swing clock. Input signal must not swing outside supply rails. |

200 | 1000 | mV |

32.768 kHz synthesized from HFCLK (LFSYNT)

| Symbol | Description | Min. | Typ. | Max. | Units | ||||

|---|---|---|---|---|---|---|---|---|---|

| fNOM_LFSYNT |

Nominal frequency |

32.768 | kHz | ||||||

| fTOL_LFSYNT |

Frequency tolerance in addition to HFLCK tolerance2 |

8 | ppm | ||||||

| tSTART_LFSYNT |

Startup time for synthesized 32.768 kHz |

100 | us |